#### Contenido

- > Conocer la herramienta *IP Integrator* para administrar IP predefinida

- Crear y reutilizar IP a nivel sistema

- Concer la herramienta IP Packager para integrar IP propia al catalogo de IP disponible

- Conocer los distintos tipos de IP disponible en el catalogo

- Usar el asistente de temporizacion para configurar y agregar recursos de temporizacion al sistema

#### **Temario**

- Herramienta IP Integrator

- Herramienta IP Packager

- o Catalogo de IP

- Asistente de Temporizacion

- Resumen

#### Diseño de sistemas con IP externa

- **▶** La IP externa suele tener distintas interfaces

- Muchas señales, mapeo complejo a archivos RTL

- La conectividad dentro del sistema no es simple

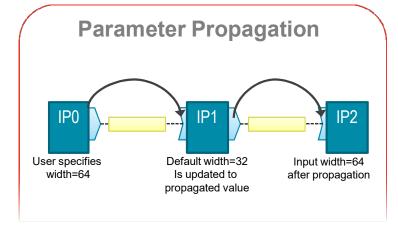

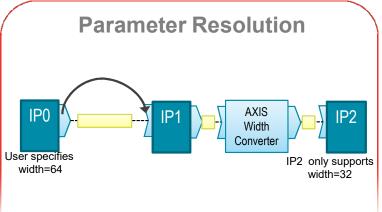

- > La IP externa es parameterizable

- El sistema debe ser consistente en las interfaces entre bloques

- Se debe tener en cuenta la interaccion entre los distintos bloques

- Puede ser necesario reutilizar parte de un sistema y ponerlo disponible para utilizar en otros proyectos

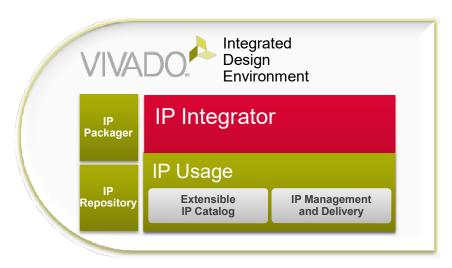

## Herramienta IP Integrator

- ➤ Es una herramienta para agregar IP externa en sistemas basados en procesadores o sistemas basados en maquinas de estado

- ➤ Tiene un entorno grafico y se puede manejar mediante scripts para configurar la IP e integrarla al sistema

#### IP Integrator

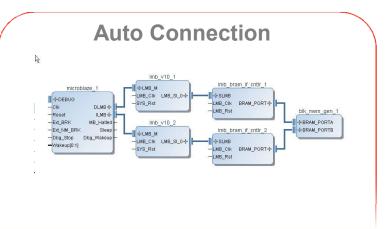

- Conectividad a nivel interface

- Se pueden administrar interfaces complejas (por ejemplo controladores de memoria)

- Se pueden crear interfaces personalizadas

- > Integracion y reutilizacion de IP

- Permite la reutilizacion de IP ya probada y depurada

- Generacion automatica de codigo fuente HDL

- La IP se integra a nivel componentes/bloques al codigo fuente

- > Permite crear sistemas basados en procesador

- Procesador, buses, perifericos y su interconexion

- Integracion con perifericos personalizados

- Se utiliza principalmente a traves de una interface grafica

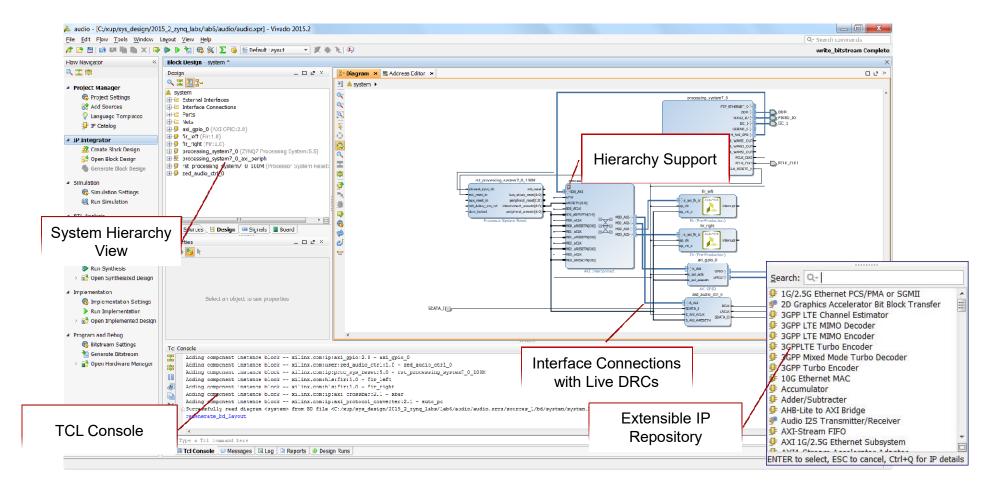

## Interface grafica de IP Integrator

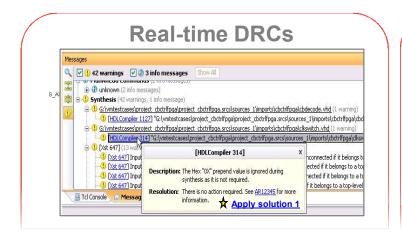

## Caracteristicas de la integracion de IP externa

#### **Temario**

- Herramienta IP Integrator

- Herramienta IP Packager

- Catalogo de IP

- Asistente de Temporizacion

- Resumen

#### Reutilizacion de IP

- ➤ Se puede integrar IP de distintas fuentes

- Toda la IP disponible en el catalgo se puede utilizar en un sistema

- ➤ Los diagramas creados con IP Integrator se pueden convertir en una sola IP, ocultando la complejidad del subsistema

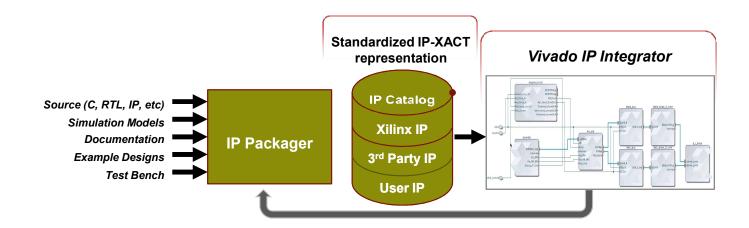

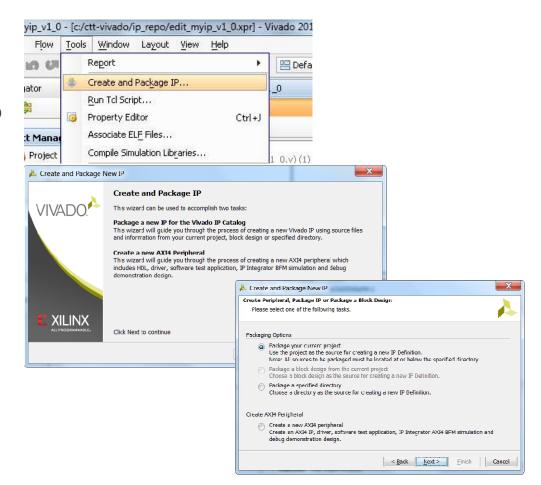

# Creacion de IP propia utilizando IP Packager

#### > Se utiliza mediante un asistente

- Automatiza el proceso de generacion de IP

- Se infiere en forma automatica la informacion adicional (simulacion, documentacion, etc)

- Se puede agregar meta-data adicional

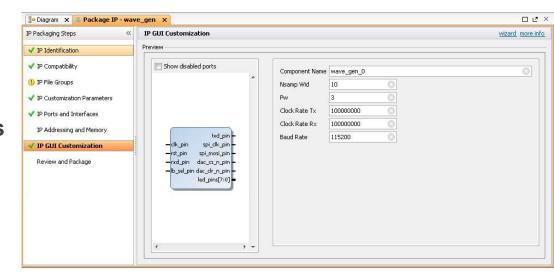

## Personalizacion de la IP propia en IP Packager

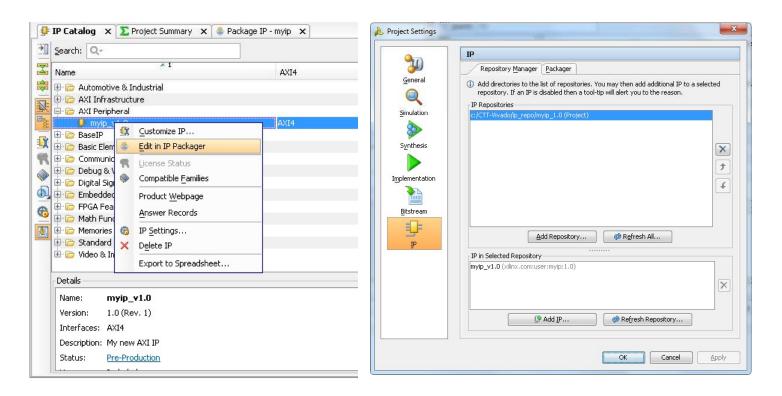

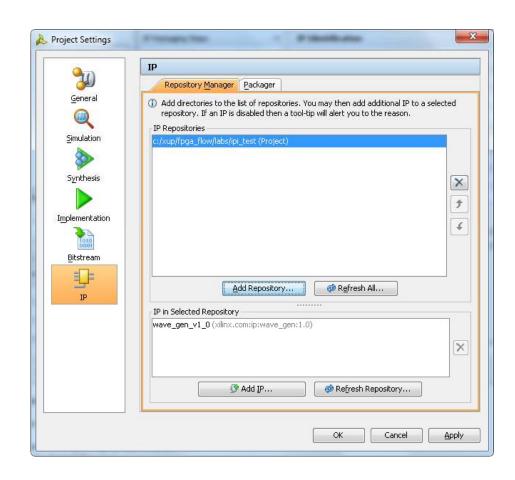

#### Reutilizacion de IP

➤ El catalogo de IP se puede ampliar agregando nuevos repositorios. Toda la IP (independientemente de su origen) se gestiona de la misma manera

#### Herramienta IP Packager

- ➤ La herramienta IP Packager permite que un modulo/bloque logico se integre al catalogo de IP para su uso o distribucion

- ➤ La IP se compone de:

- Codigo fuente

- Restricciones

- Archivos de prueba

- Documentacion

- Esta herramienta puede ejecutarse desde el entorno grafico o en forma independiente

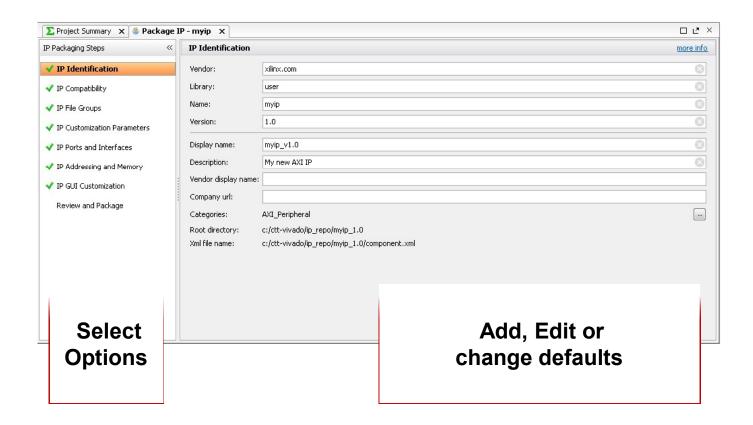

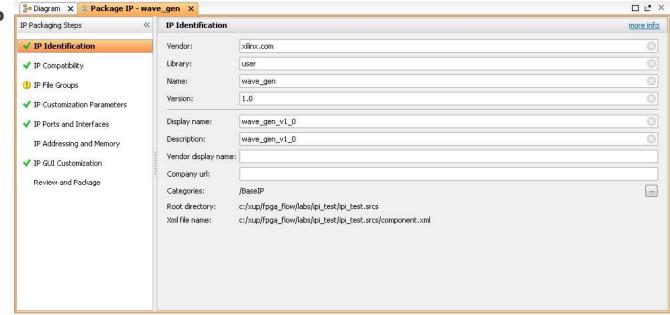

## Herramienta IP Packager

- Realiza un analisis de los archivos para determinar los parametros de la IP en forma automatica

- Genera un resumen de las caracteristicas de la IP

- > Identifica:

- Archivos fuente

- Parametros

- Puertos

- Interfases

- Crea una interface grafica para parametrizar la IP

## Herramienta IP Packager

#### ➤ Configuracion de la IP

- Propiedades

- Compatibilidad

- Archivos

- Parametros especificos

- Puertos

- Interfases

- Direccion y memoria

## Repositorios de IP

- ➤ Se crea un archivo especifico component.xml para la IP

- Se especifica la ubicacion fisica de los archivos de la IP

- > Se integra la IP al repositorio general

#### **Temario**

- Herramienta IP Integrator

- Herramienta IP Packager

- Catalogo de IP

- Asistente de Temporizacion

- Resumen

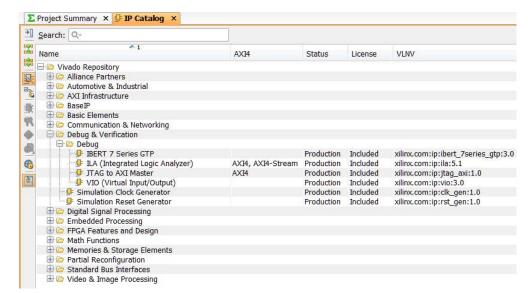

#### Catalogo de IP

- Contiene la coleccion de IP que puede utilizarse en un sistema

- Permite la construccion rapida de sistemas de caracteristicas estandard

- Cada bloque IP tiene sus propios parametros de configuracion

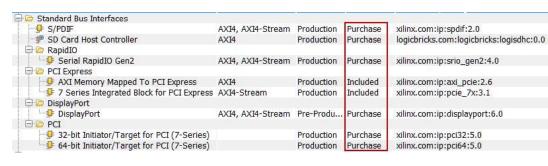

- ➤ La mayor parte de la IP es de uso libre, pero algunas requieren una licencia individual

- Se almacenan como codigo fuente en el directorio de instalación de las herramientas

- Se procesan de la misma manera que el codigo fuente HDL

- Algunas IP se almacenan encriptadas y solo se pueden integrar en la implementación

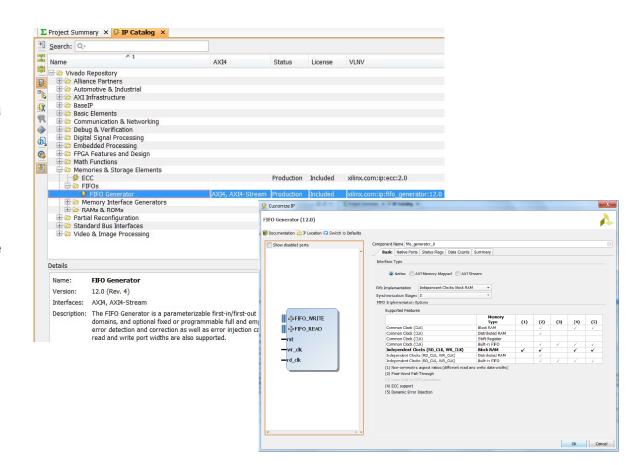

## Catalogo de IP

- Gestion de las distintas IP disponibles

- Permite la personalizacion de la IP

- Tiene una interface grafica similar a la del entorno de desarrollo Vivado

- La sintesis e implementacion se hace a traves de las herramientas de Vivado

- Puede gestionarse a traves de comandos Tcl

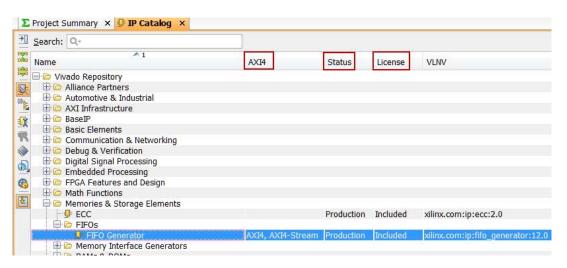

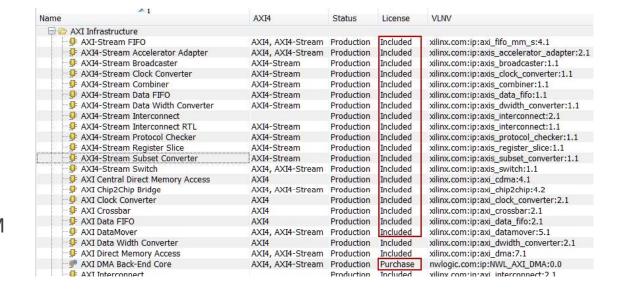

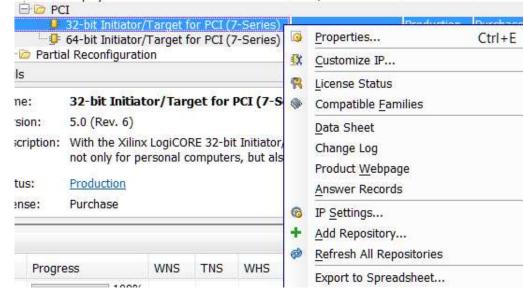

## Distintos tipos de IP disponibles

- Mucha IP en el catalogo es del tipo periferico (tiene una interfase de bus)

- Este tipo de perifericos indican el tipo de bus: AXI4 o AXI4-Stream

- La IP que no es tipo periferico no tiene entrada en la columna AXI4

- ➤ La columna "Status" indica si la IP esta en estado "production" (probada y depurada) o "pre-production" (funcionalidad probada, pero no optimizada)

- ➤ La columna "License" indica si la IP es de uso gratuito, o si es necesario adquirir una licencia adicional para su uso

#### IP Disponible para su uso sin licencia

- > Controladores de Bus y bridges

- Modulos de depuracion

- Controladores de DMA

- Timers

- Comunicacion entre procesadores (para sistemas multiprocesador)

- Controladores para memoria DRAM externa

- Perifericos para comunicaciones a alta y baja velocidad

- Otros

## IP Disponible para evaluacion (su uso requiere licencia)

- ➤ AXI CAN controller

- ➤ AXI USB2 device

- > Video IP

- > Telecoms/ Wireless IP

Se pueden utilizar con una licencia de evaluacion de 90 dias sin costo

#### Informacion de la IP

- Datos de configuracion

- Compatibilidad con las distintas familias de FPGA

- ➤ Hoja de datos (Product Guide)

- Registro de cambios (Change Log)

- Pagina web de la IP (Product Webpage)

- Informacion adicional (Answer records)

#### **Temario**

- Herramienta IP Integrator

- Herramienta IP Packager

- Catalogo de IP

- Asistente de Temporizacion

- Resumen

#### Recursos de temporizacion: MMCM y PLL

- ➤ Un dispositivo puede tener hasta 24 dominios de reloj distintos (Clock Management Tile – CMT)

- ➤ En cada CMT hay un Mixed Mode Clock Manager MMCM (Analogico y digital) y un Phase Locked Loop PLL (analogico)

- Se instancias mediante dos tipos de bloque:

- -\*\_BASE (tiene solo la interfase basica)

- -\*\_ADV (tiene la interfase completa)

- ➤ El PLL esta mas orientado a uso en interfases de I/O para controladores de memoria de alta velocidad

- ➤ El MMCM en general se utiliza para generar la termporizacion del sistema

#### Inferencia de recursos de temporizacion

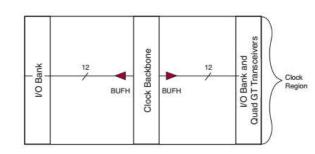

- Los ruteos de reloj se representan mediante redes en el codigo fuente RTL

- El mapeo de la red RTL al ruteo de reloj utiliza un buffer de reloj

- > Algunos recursos pueden inferirse

- Una red de entrada (con o sin un bloque IBUF instanciado) se mapeara a un ruteo de reloj global si esta red conecta a la entrada de elementos sincronizados (seria el caso de una señal de reloj externa)

- El buffer BUFG se infiere en forma automatica

- Los buffers BUFH se infieren cuando un reloj global (generado con un BUFG) es necesario en una region de reloj

- Los BUFHs de cada region se infieren automaticamente

- Los buffers BUFIO, BUFR, y BUFMR no se infieren automaticamente

- El instanciado explicito de estos buffers indica a las herramientas el uso de las redes de reloj asociadas a cada tipo de buffer

- Los bloques PLL y MMCM no se pueden inferir, se deben instanciar

UG472: 7 Series FPGA Clocking Resources

#### Instanciado de recursos de temporizacion

- Todos los recursos de temporizacion pueden instanciarse directamente en el codigo fuente RTL

- Hay modelos de simulacion para cada recurso de termporizacion

- La estructura de inferencia en Verilog/VHDL se describe en la UG953: 7Series FPGA Libraries

Guide

- Para generar la plantilla de instanciado se usa la pestaña Language Templates ( 🤝 )

- **▶** Los bloques PLL y MMCM tienen distintas opciones de interfase y atributos

- En general se instancian a traves del asistente Clocking Wizard

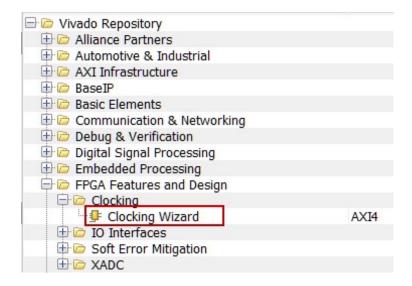

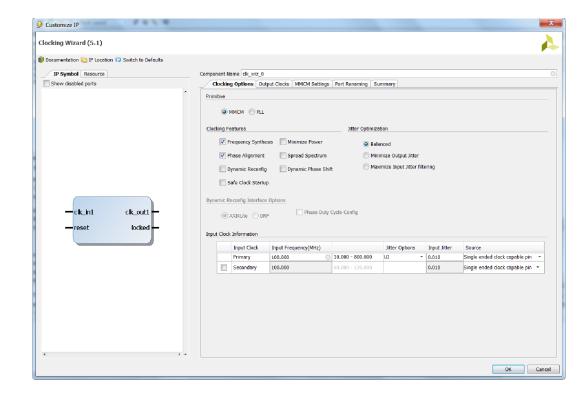

## Asistente de Temporizacion (Clocking Wizard)

- ➤ Seleccionar el catalogo IP

- Expandir la opcion FPGA Features and Design-> Clocking

- ➤ Dar doble clickn en Clocking Wizard

- ➤ El asistente realiza los pasos necesarios para generar el subsistema de temporizacion

## Asistente de Temporizacion: Opciones

- Seleccionar la primitiva a utilizar

- MMCME2 ADV

- PLLE2 ADV

- Especificar la frecuencia y tipo de entrada

- Optionalmente se puede especificar una segunda entrada

- Seleccionar las caracteristicas de la señal de reloj a generar

- Frecuencia

- Alineacion de Fase

- Desplazamiento dinamico de Fase

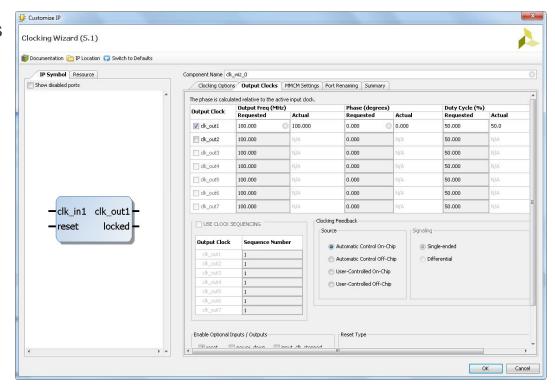

## Asistente de Temporizacion: Señales de salida

- Seleccionar la cantidad de salidas de reloj

- > Fijar las frecuencias de salida

- Opcionalmente: seleccionar otros puertos

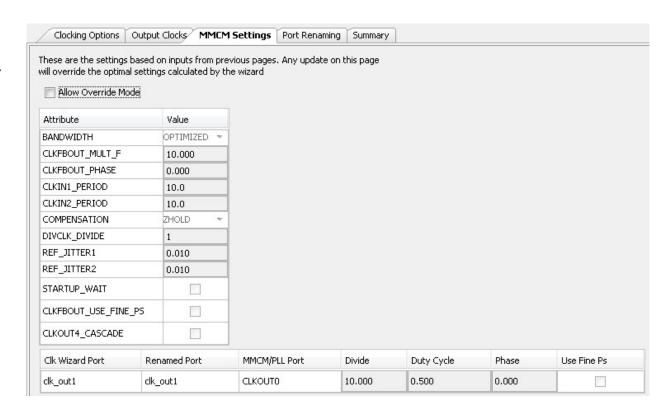

## Asistente de Temporizacion: configuracion de MMCM

- Permite sobreescribir los parametros generados por el asistente

- Permite fijar a mano la Fase, el Perido, el Jitter, etc

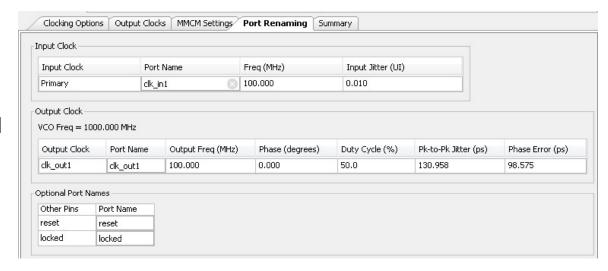

## Asistente de Temporizacion: Renombrado de los Puertos

- Permite cambiar los nombres de los puertos de entrada / salida

- Tambien se puede cambiar el nombre de los puertos opcionales

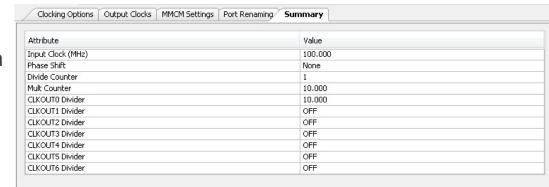

## Asistente de Temporizacion: Resumen

- Muestra las frecuencias de entrada y salida

- Otros atributos dependen de la configuración seleccionada

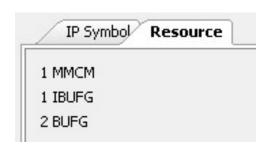

➤ La pestaña *Resource* da un resumen del tipo y numero de recursos usados

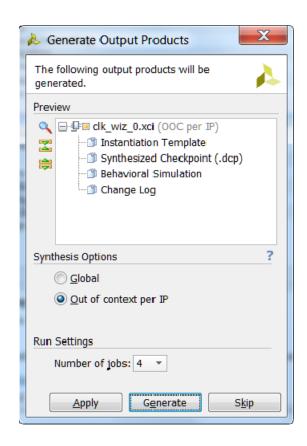

## Asistente de Temporizacion: Salidas

- Genera la plantilla de instanciado a incorporar en el codigo fuente HDL

- Modelo para el proceso de sintesis

- Modelo de simulación

- Archivos para el proceso de implementacion

- Ejemplo de uso

- Opcionalmente, una version pre-sintetizada que se puede usar directamente, sin necesidad de re-sintetizar el resto del proyecto

#### **Temario**

- Herramienta IP Integrator

- Herramienta IP Packager

- o Catalogo de IP

- Asistente de Temporizacion

- Resumen

#### Resumen

- > Se puede agregar IP a partir de liberias o crear IP propia para reutilizacion

- ➤ La herramienta IP Packagers permite genera paquetes de IP para reutilizar

- > El catalogo IP permite utilizar IP ya probada y depurada

- La IP esta agrupada de acuerdo a su funcionalidad

- ➤ El asistente de Temporizacion (Clocking Wizard) permite la configuracion y el instanciado de subsistemas de temporizacion