# UNIDAD 8: SECUENCIALES ASINCRÓNICOS.

(86:44) Técnica Digital Avanzada- Unidad 8. Profesor: Ing. Miguel Antonio Martínez.

# Secuenciales Asincrónicos.

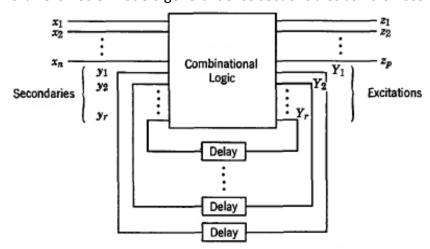

Si se eliminan los requisitos de pulsos de entrada o de pulsos de sincronismo a través de una señal de reloj para disparar las transiciones de estado se obtiene una categoría de circuitos secuenciales más versátil que se llaman circuitos con modalidad de nivel. Su forma general es un circuito lógico combinacional con realimentación. Esta realimentación alrededor de redes que, de otra manera son combinacionales, creará normalmente una operación secuencial. Comúnmente a este tipo de circuitos los llamamos secuenciales asincrónicos por no tener una señal explícita de sincronismo.

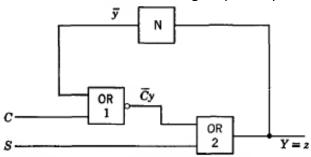

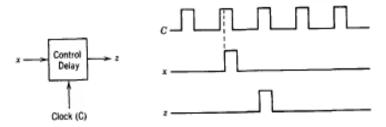

Analizaremos un circuito como el de la figura para explicar este fenómeno.

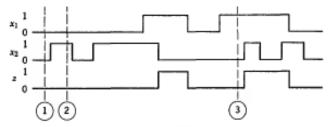

Además, presentamos un diagrama de tiempos correspondiente a este circuito que nos permitirá hacer el análisis más exhaustivo:

Como condición inicial (siempre se debe tener una en un circuito secuencial) se supondrá que tanto las entradas como la salida están en  $\mathbf{0}$ . En este caso si  $\mathbf{Y} = \mathbf{0}$  la salida de la compuerta  $\mathbf{1}$  es  $\mathbf{C'}.\mathbf{y} = \mathbf{0}$ , de manera que la compuerta  $\mathbf{2}$  ejecuta  $\mathbf{Y} = \mathbf{S} + \mathbf{C'}.\mathbf{y} = \mathbf{0} + \mathbf{0} = \mathbf{0}$ , lo cual concuerda.

En el instante  $t_1$ , S se convierte en 1. Esto hace que la salida Y de la compuerta 2 pase a 1 después de un breve retardo de propagación. A su vez y' pasa a 0 y C'.y a 1, nuevamente después de retardos breves de propagación. La compuerta 2 ejecuta 1+1=1, de manera que cuando S vuelve a 0 en el tiempo  $t_2$ , ya no hay cambios posteriores. En efecto, el término C'.y = 1 ha "asegurado" la salida en 1, de manera que S no tiene efectos subsecuentes.

A continuación, S = 0, C pasa a 1 en  $t_3$ . Esto impulsa a C'.y a 0 y a su vez, a Y a 0. A continuación y' pasa a 1, cerrando a C'.y en 0. Consecuentemente cuando C retorna a C'.y en C'.y

Considere la condición del circuito inmediatamente antes de  $t_1$ , e inmediatamente después de  $t_2$ . En ambos instantes, las entradas son las mismas, S = C

**= 0**, pero la salida es diferente. Por ende, **las salidas no dependen exclusivamente de las entradas** y el circuito es **secuencial**. Por lo tanto, no es necesario utilizar flip flop u otros dispositivos de memoria para producir circuitos secuenciales.

En este ejemplo tenemos un solo lazo de realimentación, como veremos que en este tipo de circuitos la elección de cuales variables son de realimentación, es decir de **estado** es un poco arbitraria. En los circuitos de modalidad de reloj o pulso las variables de estado son las salidas de los FF, de manera que no hay dudas sobre su identidad. En los circuitos con modalidad de nivel, los lazos de realimentación forman trayectorias continuas y la parte de dicho lazo que se desee identifica con las variables de estado queda a elección.

Ahora veremos el modelo general de los secuenciales asincrónicos.

Recordar que los elementos de retardo no son, por regla, elementos específicos insertados en la trayectoria de la realimentación para ese fin, sino que más bien representan una "concentración" de los retardos distribuidos en los elementos lógicos combinacionales. Se puede considerar que estos elementos de retardo proporcionan una memoria a corto plazo. Cuando cambia una entrada, el retardo le permite "recordar" los valores actuales de las variables  $y_1, y_2, \dots, y_n$  un tiempo suficientemente largo para desarrollar nuevos valores de Y<sub>1</sub>, Y<sub>2</sub>,......, Y<sub>n</sub> que, a su vez se convierten en los valores del siguiente estado de y después del retardo. Se observará la distinción hecha entre las y y las Y. En la condición de estado estacionario, son iguales, pero durante la transición no lo son. Las y se denominaran secundarias y a las Y las llamaremos excitaciones. Ambas corresponden a las variables de estado en los circuitos con modalidad de reloj. En el diagrama de tiempos se observa que los cambios en los secundarios y las excitaciones, es decir, los cambios de estado se pueden producir en respuesta a cualquier cambio en el valor de las entradas. En más, en ese ejemplo se permite que cambie una variable a la vez, y no se margen para que ocurra ningún otro cambio hasta que todas las variables hayan quedado estabilizadas. Cuando se pueden implantar estas restricciones en las entradas el circuito, se dice que dicho circuito opera en modalidad fundamental. Aunque la modalidad fundamental es un método de operación y no un tipo especial de circuito, se hará referencia a circuitos diseñados con esta imposición, como circuitos con modalidad fundamental.

## Síntesis de Secuenciales Asincrónicos.

Esta vez no haremos el análisis de un circuito asincrónico, sino que pasaremos directamente al diseño. Análogamente al diseño secuencial sincrónicos acá partiremos de algo parecido a una tabla de estados, pasaremos a una tabla de transición y al circuito final.

La tabla de estado de comienzo la llamaremos **Tabla de Flujo**. La posibilidad de cometer errores en el proceso de traducir las proposiciones del problema en una tabla de flujo se minimiza yendo inicialmente a una **Tabla de Flujo Primitiva**.

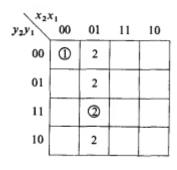

Se define como **tabla primitiva** aquella que tiene un solo **estado estable por renglón**. Por ejemplo, una tabla de flujo primitiva de algún problema podría ser como la de la figura siguiente:

| SC |    |    |    | 1  |   |

|----|----|----|----|----|---|

|    | 00 | 01 | 11 | 10 | z |

|    | 0  | 4  | j  | 2  | 0 |

|    | 3  |    | -  | 2  | ı |

|    | 3  | 4  |    | 2  | 1 |

|    | 1  | 4  | -  | -  | 0 |

En los problemas de modalidad fundamental, frecuentemente conviene representar primero el problema como una gráfica de tiempo, en lugar de hacer un diagrama de estado. Veremos un ejemplo donde se plasma esta idea.

**Ejemplo:** Se desea diseñar un circuito con modalidad fundamental con dos estados,  $x_1$  y  $x_2$  y una salida z. La salida del circuito debe ser 0 siempre que  $x_1 = 0$ . El primer cambio en la entrada  $x_2$ , que ocurre mientras  $x_1 = 1$ , hará que la salida del circuito pase a 1. Entonces, la salida debe permanecer en 1 hasta que 1 vuelva a 10. Los cambios en las entradas estarán siempre lo suficientemente separadas en el tiempo para permitir que el circuito se estabilice antes de que se produzca una segunda transición de entrada. En la figura se ilustran algunas secuencias típicas de entrada y salida.

El primer paso del proceso de diseño consiste en determinar una tabla de flujo primitiva, para lo cual se debe suponer algún estado estable de iniciación conveniente. En este caso, es más conveniente seleccionar un estado para el que  $\mathbf{x}_2\mathbf{x}_1 = \mathbf{00}$ . Para este estado, la salida será  $\mathbf{0}$  sin importar cuál fue la última entrada en cambiar. Este estado inicial se indica como  $\mathbf{1}$  con un círculo por alrededor en la siguiente figura:

| 1.52.1 | 00 | 01 | 11 | 10 |

|--------|----|----|----|----|

|        | Φ  | 3  |    | 2  |

|        | 1  |    | 4  | 0  |

|        | 1  | 3  |    | -  |

|        | -  |    | 4  |    |

| 1  |    |       |        |

|----|----|-------|--------|

| 00 | 01 | _11   | 10     |

| 0  |    |       |        |

|    |    |       | 0      |

|    | 0  |       |        |

|    |    | 0     |        |

|    | 00 | 00 01 | 0 0 11 |

También se señala la salida para el estado estable. Por ahora solo se indicarán las salidas correspondientes a los estados estables de la tabla de flujo. Puesto que no se permite que las dos entradas cambien simultáneamente se anota un guion en la columna correspondiente a  $\mathbf{x_2x_1} = \mathbf{11}$  del primer renglón de la tabla. Así se anotarán guiones en cada renglón de la tabla de flujo primitiva que difiera en las dos entradas de las entradas correspondientes al estado estable de dicho renglón.

Si  $x_2$  pasa a 1, mientras  $x_1$  sigue siendo 0, no se tendrá ninguna salida del circuito, así que dejará que pase a un estado estable 2 con circulo con z = 0. Si  $x_1$  pasa a 1, mientras  $x_2 = 0$ , el circuito pasa a un estado estable 3, también con z = 0. Partiendo del estado estable 2, al volver  $x_2$  a 0, hará que el circuito retorne al estado estable 1, como lo hará 10 desde el estado 13.

Partiendo del estado **2 estable** cuando  $x_1$  pasa a **1**, hará que el circuito llegue a un estado nuevo **4**, también con z = 0. Hasta ahora en la figura anterior es una tabla primitiva parcial porque faltan otras alternativas. Las entradas no circuladas, es decir, los **estados inestables**, se limitan a representar el destino del circuito después de una transición de entrada.

Los estados 3 y 4 corresponden al último cambio que se produjo de  $x_1 = 0$  a  $x_1 = 1$ , de tal manera que un cambio en  $x_2$  hará que la salida pase a 1, lo cual origina la transición a 5 con z = 1. Igualmente, del estado 4, al pasar  $x_2$  a 0, produce un pase a 6 con z = 1. A partir del estado 4, cuando 4, cuando 4, el circuito volverá al estado anterior 4. Estas adiciones a la tabla de flujo primitiva se ilustran en la figura siguiente:

|        |    |    | -   | •  |

|--------|----|----|-----|----|

| 1.12.1 | 00 | 01 | 11  | 10 |

| •      | 0  | 3  | -   | 2  |

|        | 1  | -  | 4   | 2  |

|        | 1  | 3  | 5   | -  |

|        | -  | 6  | 4   | 2  |

|        |    |    | (3) | i  |

|        |    | 6  |     |    |

|        |    |    |     |    |

| X <sub>2</sub> X | 00 | 01 |   | 10 |

|------------------|----|----|---|----|

|                  | 0  |    |   |    |

|                  |    |    |   | 0  |

|                  |    | 0  |   |    |

|                  |    |    | 0 |    |

|                  |    |    | 1 |    |

|                  |    | 1  |   |    |

A partir de cualquiera de los estados 5 o 6, la salida debe mantenerse en 1, siempre y cuando  $x_1$  siga siendo 1, sean cuales fueren los cambios subsecuentes en  $x_2$ . Así pues, se proporcionan los estados 7 y 8, ambos con z = 1, de tal manera que el circuito formará un ciclo entre 5 y 7, o bien entre 6 y 8, para cambios consecutivos en  $x_2$ . Esto se muestra en la siguiente figura:

| X2.X | 00 | 01 | 11  | 10 |

|------|----|----|-----|----|

|      | Φ  | 3  | -   | 2  |

|      | 1  | -  | 4   | 0  |

|      | 1  | 3  | 5   | -  |

|      | -  | 6  | 4   | 2  |

|      | -  | 7  | (3) | 2  |

|      | 1  | 6  | 8   | -  |

|      | 1  | Ø  | 5   | 1  |

|      | -  | 6  | 8   | 2  |

| X2X | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

|     | 0  |    |    |    |

|     |    |    |    | 0  |

|     | _  | 0  |    |    |

|     |    |    | 0  |    |

|     |    |    | 1  |    |

|     |    | 1  |    |    |

|     |    | 1  |    |    |

|     |    |    | 1  |    |

|     |    |    |    |    |

Que representa la tabla de flujo primitiva final. Si se compara la tabla de flujo primitiva con una tabla de estado típica, se observa una diferencia notable, la ausencia de una columna de estado actual en la tabla de flujo.

Esta diferencia se deriva del hecho que en un circuito de reloj es estable solo entre los pulsos de reloj, y en ese instante el estado del circuito es independiente de las entradas presentes. Por lo tanto, todos los estados estables se pueden agrupar en una columna correspondiente a una entrada sin reloj. Un circuito con modalidad fundamental será estable todo el tiempo que todas las entradas sean así mismo estables, y el estado dependerá del valor de las entradas. Po ende, la anotación de estado presente puede aparecer en cualquier columna de la tabla de flujo.

Veremos cómo minimizar una tabla de flujo primitiva, usaremos las mismas técnicas que vimos en circuitos secuenciales sincrónicos. La única diferencia es que esta tabla corresponde a un circuito no totalmente especificado, por lo tanto, en vez de equivalencia hablamos de compatibilidad. Primero escribimos nuevamente la tabla:

| q*        | 00                      | 01 ×2                                | x <sub>1</sub>                      | 10                              | 00 | 01 | x,     | 10 |

|-----------|-------------------------|--------------------------------------|-------------------------------------|---------------------------------|----|----|--------|----|

| 800000000 | ① I I - I I I I I I I I | 3<br>-<br>3<br>6<br>7<br>6<br>7<br>6 | - 4 5 <b>(4)</b> (5) 8 5 <b>(8)</b> | 2<br>2<br>2<br>2<br>-<br>-<br>2 | 0  | 0  | 0<br>1 | 0  |

|           |                         | q*                                   | +1                                  |                                 |    | -  |        |    |

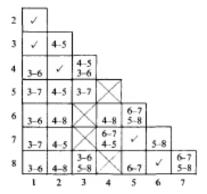

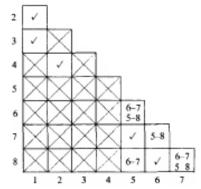

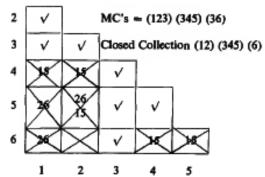

Ahora usaremos las tablas de implicación ya vista para circuitos sincrónicos, nos queda la siguiente tabla:

Usando las técnicas antes conocidas llegamos a:

Eliminando todos los pares incompatibles, nos quedan las clases compatibles máximas que son las siguientes:

La colección cerrada más pequeña se puede encontrar mediante una inspección, y es:

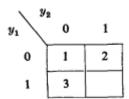

En la siguiente figura se ve una tabla de tres estados correspondientes a la colección cerrada indicada en último término.

|        |          |    | x <sub>2</sub> x <sub>1</sub> |          |          |    | x2X1 |    |    |  |

|--------|----------|----|-------------------------------|----------|----------|----|------|----|----|--|

|        | $q^{v}$  | 00 | 01                            | 11       | 10       | 00 | 01   | 11 | 10 |  |

| (13)   | @        | @  | @                             | с        | b        | 0  | 0    | _  | 0  |  |

| (24)   | <b>6</b> | а  | c                             | <b>6</b> | <b>®</b> | 0  | -    | 0  | 0  |  |

| (5678) | @        | а  | 0                             | @        | ь        | _  | 1    | 1  | -  |  |

|        |          |    | $q^{r}$                       | + 1      |          |    | :    |    |    |  |

Algo importante es que, si una variable de salida cambia de valor como resultado de una transición de estado, entonces dicha variable es **opcional** durante dicha transición. A continuación, al hacer la asignación de estados hay que tener algunos cuidados porque pueden aparecer lo que se llama **ciclos y carreras.**

Antes de definir estos fenómenos (ciclos y carreras) veremos un ejemplo donde aparece uno de ellos.

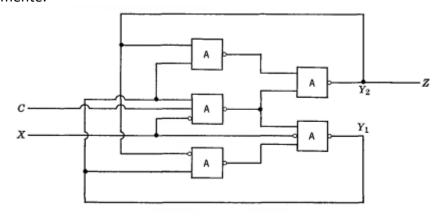

Para ello desarrollaremos un retardo de control como el de la figura:

Este circuito recibe pulsos de, aproximadamente, el mismo ancho de los pulsos de reloj. Por cada pulso de entrada  $\mathbf{x}$  debe haber un pulso de salida  $\mathbf{z}$ , que coincida con el siguiente pulso de reloj que sigue al pulso  $\mathbf{x}$ .

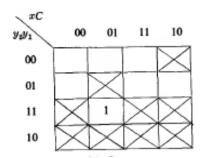

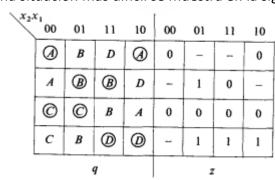

Presentamos la tabla primitiva completa en la siguiente figura;

| $\sqrt{x}C$ | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 |

|-------------|----|----|----|----|----|----|----|----|

|             | 0  | 2  | -  | -  | 0  |    |    |    |

|             | 1  | 2  | 3  | -  |    | 0  |    |    |

|             | -  | ** | 3  | 4  |    |    | 0  |    |

| 1           | 5  | -  | _  | 4  |    |    |    | 0  |

|             | ூ  | 6  | -  | -  | 0  |    |    |    |

|             | 1  | 6  | -  | -  |    | ı  |    |    |

|             |    |    |    |    |    |    | z  |    |

La tabla de implicación como así también una cobertura y una colección cerrada se visualiza a continuación:

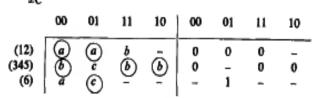

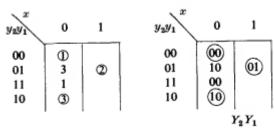

Con lo cual llegamos a la tabla de flujo mínima para este ejemplo:

La siguiente etapa del diseño consiste en asigna combinaciones específicas de los secundarios a los renglones de la tabla de flujo reducida. En este caso se tienen todos los problemas de asignación de estados de los circuitos con modalidad de reloj, además de algunos problemas especiales que son peculiares de la modalidad fundamental. Primero se asignan las combinaciones de los valores secundarios  $y_2y_1 = 00$  a a,  $y_2y_1 = 01$  a b y  $y_2y_1 = 11$  a c. Sustituyendo los valores estables en la tabla de flujo reducida nos queda:

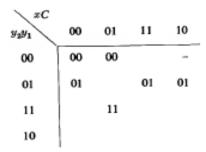

Y nos quedan las tablas completas para los estados:

| $y_2y_1$ | 00       | 01          | 11       | 10       |

|----------|----------|-------------|----------|----------|

| 00       | 00       | <b>∞</b>    | 01       | $\times$ |

| 01       | (01)     | 11          | (01)     | (0)      |

| 11       | 00       | (1)         | $\geq$   | $\times$ |

| 10       | $\times$ | $\boxtimes$ | $\times$ | $\times$ |

Y para la salida z:

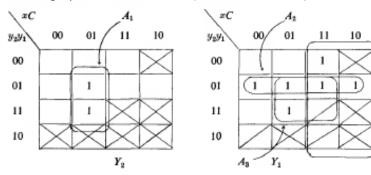

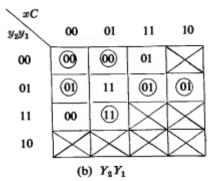

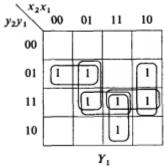

Para hallar las ecuaciones de excitación dividimos la tabla de estados en diagramas de Karnaugh para cada variable (en este caso dos).

Resolviendo estos llegamos a las ecuaciones:

$$Y_2 = \bar{x}Cy_1$$

$Y_1 = x + \bar{y}_2y_1 + Cy_1$

$z = y_2$

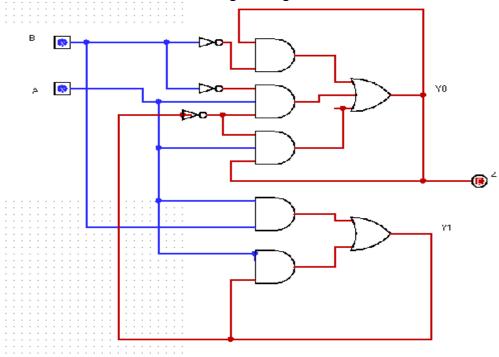

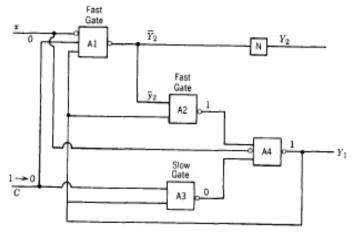

Dibujando el circuito correspondiente a estas ecuaciones nos queda:

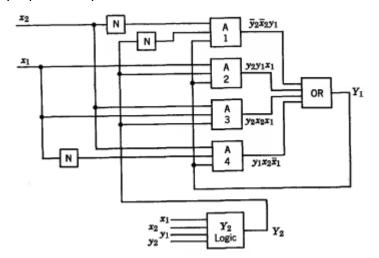

Analizaremos en detalle el funcionamiento de este circuito. Supongamos que el circuito se encuentra en el estado estable s.C. $y_2.y_1 = 0111$ , correspondiente al estado estable c en la segunda columna y tercera fila de la tabla de estado. En la figura anterior se puede ver los valores correspondientes en varios puntos del circuito. Se observará que los valores c para c y c y c están producidos por las compuertas c y c c respectivamente. Ahora suponga que c pasa de c c c c c c en el tercer renglón al estado estable c c de la primera columna, primer renglón, cambiando las dos variables de estado a c c c

Recordando que una compuerta NAND emitirá un  ${\bf 1}$  si cualquier entrada es  ${\bf 0}$ , se observará que la señal C=0 excitará las salidas de  $A_1$  y  $A_3$ . Con la condición de que  $A_2$  no cambie demasiado rápidamente, el 1 en la salida de  $A_3$  excitará entonces a  $Y_1$  para que pase a 0 en la salida de  $A_4$ . Este valor de  $Y_1$  alimentado nuevamente a la entrada de  $A_2$ , cerrará su salida en 1 estabilizando, a su vez, a  $Y_1$  en 0, como se requiere.

No obstante, suponga ahora que las compuertas tienen retardos desiguales, como se ilustra en el circuito dibujado. En este caso, el cambio en C impulsará primero la salida de  $A_1$  a 1, que a su vez hará que  $A_2$  pase a 0, antes de que la salida de  $A_3$  pase a 1. Como resultado,  $Y_1$  no cambiará y el circuito efectuará una transición errónea a  $Y_2Y_1$  = 01, que es el estado estable b de la primera columna.

El problema que se acaba de descubrir ocurrió debido a que los dos secundarios debían cambiar simultáneamente, después de un solo cambio de entrada, pero no los hicieron simultáneamente a causa de los retardos desiguales del circuito. Está situación se llama "carrera" porque la naturaleza de la transición puede depender de cuál sea la variable que cambia más rápidamente. Ahora estudiaremos la naturaleza de estas carreras y como se pueden eliminar mediante una mejor asignación de estados.

# Ciclos y carreras.

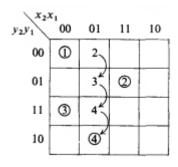

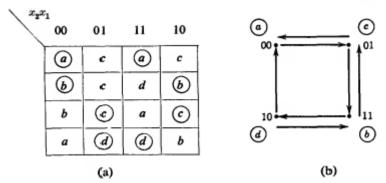

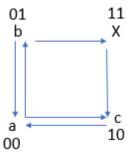

Un circuito puede asumir más de un estado inestable antes de llegar a un nuevo estado estable. Si para un estado inicial dado y una transición de entrada, este tipo de secuencia de estados inestables es única, se lo denomina **ciclo**.

Por ejemplo, en la siguiente figura:

En este caso el circuito seguirá un ciclo a través de tres estados inestables durante una transición de  $\bf 1$  a  $\bf 4$ . En la tabla de la derecha se ve que el siguiente estado para  $y_2y_1x_2x_1=0001$  no es  $y_2y_1=10$ . Por el contrario, la maquina procede de 00 a 01 a 11 a 10. Cada una de las transiciones implica el cambio en un solo secundario. De donde el circuito procede con seguridad a través de cada uno de los estados inestables hasta llegar al estado estable final. El ciclo se puede anotar también partiendo de los estados estables  $\bf 2$  y  $\bf 3$ .

Cuando el mapa Y especifica un cambio de más de un secundario, la situación resultante se denomina **carrera**. Veamos la siguiente situación:

Supongamos que las entradas cambian a 01 mientras la máquina se encuentra en el estado  $y_2y_2 = 00$ . Si  $y_2$  cambia primero, la maquina pasa al estado inestable 10. Si  $y_1$  cambia primero, la maquina pasa a 01. Para cualquiera de estos estados inestables, el mapa Y indica que es siguiente estado es el estable 2. Por ende, sea cual fuere el resultado de la carrera se llega siempre al estado estable 2. Este tipo de carrera lleva el nombre de carrera no crítica.

La situación encontrada en el ejemplo del retardo de control es un caso de carrera crítica, que es una situación cuando en la cual se tienen dos o más estados estables en una columna dada y, el estado final al que llega el circuito depende del orden en que cambian las variables. En otras palabras, el resultado deseado puede producirse o no, dependiendo de los retardos reales del circuito.

En la siguiente figura vemos el ejemplo de otra carrera crítica. En este caso se supone que el circuito pase del estado  $\mathbf{2}$  ( $y_2y_1=01$ ) en la columna x=1, al estable  $\mathbf{3}$  ( $y_2y_1=10$ ) en la columna x=0. Si  $Y_1$  cambia primero, las excitaciones serán  $Y_2Y_1=00$ , llevando a una transición errónea al estable  $\mathbf{1}$ . Por otro lado, si  $Y_2$  cambia primero, las excitaciones serán  $Y_2Y_1=11$ , lo cual conducirá a  $\mathbf{1}$  inestable en el tercer renglón, y de allí al estado estable  $\mathbf{1}$ . En consecuencia, sean cuales fueran los retardos, se producirá la transición equivocada.

Podría parecer que el primer tipo de carrera crítica es menos problemática, ya que, teóricamente, se puede eliminar mediante un ajuste adecuado de los retardos. Sin embargo, en la práctica, es difícil y costoso restringir los retardos, de manera que se deben evitar las dos clases de carreras críticas, En algunos problemas, esto se puede lograr mediante la asignación correcta de las variables de estado. En otros, es necesario utilizar más de un número mínimo de estados.

Ahora lo que haremos es volver al ejemplo del retardo de control visto anteriormente con los problemas que este tiene de la forma que lo hemos diseñado. Construiremos una versión mejorada del mismo, para ello lo que hay que eliminar es la carrera crítica que aparece en la columna 00, Volvemos a mostrar la tabla de transición de ese circuito.

Reemplazamos esta carrera crítica por un ciclo usando el estado adicional, esto se muestra en la siguiente figura donde también vemos el mapa de salida del circuito.

Lo que hicimos es reformar la tabla de transición nueva. Los cambios se visualizan en los dos cuadrados inferiores de la columna xC = 00. Por lo tanto, a partir del estado estable **11**, el circuito seguirá el ciclo que se indica mediante flechas, cuando C pase a 0. De acuerdo con los mapas de excitación, el único cambio es un 1 adicional en el tercer renglón. La nueva ecuación para  $Y_2$  es:

$$Y_2 = y_2 y_1 + \bar{x} C y_1$$

No se produce ningún cambio en la ecuación de  $Y_1$ . Para evitar un pulso de salida posible durante el ciclo, se debe especificar un 1 adicional en el mapa de salida como se indica en la figura anterior, pero esto no cambia la ecuación correspondiente a z. El

circuito revisado para el retardo de control se muestra en la siguiente figura. El circuito funcionará correctamente como retardo de control, a condición de que los pulsos de entrada satisfagan las restricciones de la modalidad fundamental que se resumieron anteriormente.

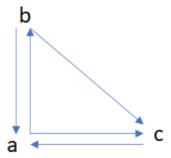

# Asignaciones de carrera libre.

Para eliminar las carreras críticas, se deben asignar las variables de estado de tal manera que las transiciones entre estados requieran que solo cambie una variable a la vez. Con este objeto, es conveniente que los estados estables entre los cuales se producen transiciones tengan asignaciones adyacentes, es decir, asignaciones que difieran en una sola variable. Para encontrar dichas asignaciones, es conveniente elaborar un diagrama de transición en el hipercubo booleano.

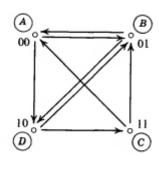

Ahora analizaremos la siguiente tabla de estado como así también el diagrama de transición.

Se comienza asignando 00 al estado **a**. Si se observa que **ha** tiene transiciones a **c**, a **c** se le da la asignación adyacente 01 y dicha transición se indica con una flecha que une **a** con **c**. A continuación, la transición de **c** nuevamente a **a**, se indica con una flecha que va de **c** a **a**. Dado que existe una transición de **c** a **b**, esta última recibe una asignación adyacente en 11, dejando 10 para **d**. A continuación, el diagrama se completa llenando las flechas para todas las transiciones restantes. En este caso, todas las transiciones quedan entre estados adyacentes, de manera que esta asignación quedará **libre de carreras críticas.**

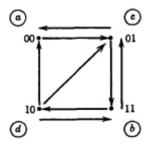

Otra situación algo diferente es la que vemos en la siguiente figura:

En este caso **d** tiene una transición a **c**, dando en como resultado una transición diagonal, esto es, un cambio de dos variables. Obsérvese que esta transición diagonal no se puede eliminar, ya que **d** tiene transiciones a otros tres estados y no puede ser adyacente a todos ellos con solo dos variables de estado. No obstante, se observa que esta transición diagonal representa una **carrera no crítica** y no causará problemas, Siempre que haya solo un estado estable en una columna, no es necesario considerar las transiciones a dicha columna al escoger una asignación de estado, ya que las carreras críticas no se pueden producir a menos que existan por lo menos dos anotaciones estables en una columna.

Una situación más difícil se muestra en la siguiente figura:

Acá se encuentran varias carreras críticas, como lo muestran las transiciones diagonales, y es evidente que ninguna permutación de la asignación puede eliminar todas las transiciones diagonales. Por ejemplo, el primer renglón requiere que tango **B** como **D** sean adyacentes a **A**, en tanto que el segundo renglón establece que **B** y **D** sean adyacentes. Por supuesto, no se pueden satisfacer todos estos requisitos.

En situaciones como la que se acaba de describir, las carreras críticas solamente se pueden eliminar utilizando los estados de reserva. Si el número de estados de la tabla original de estado no es una potencia de dos, se dispondrá automáticamente de estados de reserva. Este fue el caso del retardo de control, en donde había solo tres estados, y el estado de reserva se utilizó para realizar un ciclo, evitando así una carrera crítica. Si el numero original de estados es una potencia de dos, o sí no se encuentra una asignación satisfactoria empleando los estados de reserva disponibles, la única solución es crear más estados agregando variables de estado adicionales.

Hay dos técnicas básicas para utilizar los estados de reserva, las asignaciones de **renglón compartido** y la de **renglones múltiples**. Esta última, como su nombre lo indica, a cada estado se le asigna dos o más combinaciones de variables de estado, es decir dos o más renglones de una tabla de transición. Este método de asignación de renglones múltiples requiere siempre variables de estado adicionales, ya que la cantidad de renglones debe ser al menos el doble que el número de estados. Esto incrementa mucho

el costo, por lo tanto, se trata de no usar este método a menos que no quede otra alternativa. Por esa razón no lo desarrollaremos.

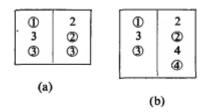

Veremos solo el método de **renglones compartidos.** Este método lo que hace es no asignar los renglones adicionales a ningún estado específico, sino que por el contrario quedan **compartidos** como sea necesario, con el objeto de convertir cualquier carrera crítica ciclos de transiciones adyacentes. Para tablas de tres estados, cualquier asignación como la que muestra la siguiente figura conducirá a una realización de renglones compartidos y libre de carreras críticas.

Cualquier transición entre 1 y 2 o entre 1 y 3 es adyacente, y las transiciones entre 2 y 3 siguen un ciclo a través del renglón de reserva. Esta asignación ya la utilizamos en el ejemplo del retardo de control. En tablas de cuatro renglones no se contará con renglones de reserva, a menos que se añada una variable de estado.

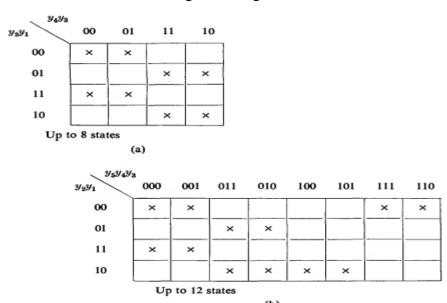

Casi todas las máquinas de cinco se pueden manejar empleando tres variables de estado. Una asignación universal para **n** estados es tal, que funcionará para cada flujo de estado **n** y cualquier numeración de estados. Las asignaciones universales para 5 a 8 estados y 9 a 12 estados se ven en las siguientes figuras:

Puesto que solo se tiene un renglón por estado y la numeración no es arbitraria, en la figura anterior no se indican los números de estado sino solamente se señalan con una  $\mathbf{x}$  los renglones a los cuales se deben asignar los estados. Para una cantidad de 5 a 8 estados, asigne simplemente un renglón con  $\mathbf{x}$  de la figura (a) a cada estado, y haga lo mismo para los estados 9 a12 de la figura (b).

Un concepto útil para encontrar esta clase de asignaciones es el llamado **conjunto de destino**. En cualquier columna en una tabla de estados, el conjunto destino consiste en cualquier estado estable y cualquier renglón que produzca transiciones hacia dicho estado. Por ejemplo, en la siguiente figura:

| $x_2x$ | 'n |    |    |          |    |    |    |    |

|--------|----|----|----|----------|----|----|----|----|

|        | 00 | 01 | 11 | 10       | 00 | 01 | 11 | 10 |

| 1      | 0  | 3  | 4  | <b>①</b> | 0  | -  | 0  | 0  |

| 2      | 5  | 4  | 2  | 2        | -  | 1  | 1  | 0  |

| 3      | 3  | 3  | 2  | 1        | 1  | 1  | 1  | -  |

| 4      | 1  | 4  | 4  | 4        | _  | 1  | 0  | 1  |

| 5      | 3  | 3  | 3  | 4        | 0  | 1  | 1  | 1  |

|        |    | a  |    |          |    |    |    |    |

States

En la primera columna los estados estables son 1, 3 y 5. El renglón 4 lleva a 1, y la hilera 2 lleva a 5. Por lo tanto, los conjuntos de destino para esta columna son (1, 4) (2, 5) (3), lgualmente, los estados de destino para la segunda, tercera y cuarta columna son: (1, 3) (2, 4) (5) (1, 4) (2, 3) (5) y (1, 3) (2) (4, 5), respectivamente. Los conjuntos de destino son importantes porque, para evitar carreras críticas, los miembros de cada conjunto deber ser adyacentes o estar localizados en esta forma en relación con los estados adicionales para las transiciones cíclicas para todos los conjuntos de una columna dada se puedan efectuar sin interferencias.

En la siguiente figura se muestra una asignación estándar para tablas de cinco estados. Se la llama "estándar" y no "universal" debido a que funcionará para casi cualquier tabla, pero fallará en algunos casos, como veremos luego.

| y3y            | 2  |    |    |    |

|----------------|----|----|----|----|

| y <sub>1</sub> | 00 | 01 | 11 | 10 |

| 0              | ×  |    | ×  |    |

| 1              | ×  | ×  | ×  |    |

Para este caso numeramos arbitrariamente los cinco estados como se muestra en el mapa de Karnaugh y en el hipercubo booleano.

| y <sub>3</sub> y | 2  |    |    |    |

|------------------|----|----|----|----|

| $y_1$            | 00 | 01 | 11 | 10 |

| 0                | 1  |    | 5  |    |

| 1                | 2  | 3  | 4  |    |

En la primera columna de la tabla de estados, los conjuntos de destino son (1, 4) (2, 5) (3), requiriendo transiciones de 4 a 1 y de 2 a 5. Se observa en el hipercubo que estas transiciones son imposibles con la esta asignación, ya que los dos ciclos deben utilizar los mismos renglones de reserva en su trayectoria de destinos diferentes. Los renglones pueden ser **compartidos** solo en el sentido de que se puedan usar para

diferentes ciclos en diferentes columnas. En cualquier columna dada, un renglón de transición puede formar parte de un ciclo que vaya a un solo destino.

El problema del ejemplo anterior se puede solucionar permutando las asignaciones de tal manera que los dos conjuntos de dos miembros no ocupen diagonalmente vértices opuestos del hipercubo. Por lo tanto, el mapa queda así:

Para la tabla de estados dada, asignamos (1, 2) y (3, 5) a las ubicaciones diagonales, como se indica en el siguiente gráfico:

| √ y <sub>3</sub> 3 | /2  |    |    |    |

|--------------------|-----|----|----|----|

| y <sub>1</sub>     | 00  | 01 | 11 | 10 |

| 0                  | (1) | α  | ③  | β  |

| 1                  | 3   | 4  | 2  | γ  |

Para mayor facilidad de referencia, los renglones de reserva se marcan como  $\alpha$ ,  $\beta$  y  $\gamma$ . Para formular la tabla de estado aumentada, se empieza llenando los estados estables y las salidas correspondientes. Esta tabla aumentada genérica se muestra en la siguiente figura.

| $x_2x$ | 'n       |          |    |    |    |    |    |    |

|--------|----------|----------|----|----|----|----|----|----|

|        | 00       | 01       | 11 | 10 | 00 | 01 | 11 | 10 |

| 1      | Φ        | 3        | 4  | 1  | 0  | -  | 0  | 0  |

| 2      | 5        | 4        | 2  | 2  | -  | 1  | 1  | 0  |

| 3      | 3        | 3        | 2  | 1  | 1  | 1  | 1  | -  |

| 4      | 1        | 4        | 4  | 4  | _  | 1  | 0  | 1  |

| 5      | <b>3</b> | <b>③</b> | 3  | 4  | 0  | 1  | 1  | 1  |

|        |          | Ctotoo   |    |    |    |    |    |    |

Las anotaciones de transición se llenan haciendo referencia al mapa de la asignación siguiente:

| y <sub>3</sub> 3 | /2 |    |    |    |

|------------------|----|----|----|----|

| $y_1$            | 00 | 01 | 11 | 10 |

| 0                | ①  | α  | ③  | β  |

| 1                | 3  | 4  | 2  | γ  |

Esta figura sirve para determinar si la transición es directa o sí se debe proporcionar un ciclo a través de estados de reserva. El estado  ${\bf 1}$  efectúa transiciones a  ${\bf 3}$  en la columna 01 y a  ${\bf 4}$  en la columna 11. La transición a  ${\bf 3}$  es directa, pero la transición a  ${\bf 4}$  utiliza el ciclo  ${\bf 1} \rightarrow \alpha \rightarrow {\bf 4} \rightarrow {\bf 4}$ , como se observa en la tercera columna de la siguiente tabla:

|          | \ 2                           | $x_{2}^{2}$ |          |          |    |    |    |    |     |

|----------|-------------------------------|-------------|----------|----------|----|----|----|----|-----|

| $y_3$    | 1 <sub>2</sub> y <sub>1</sub> | 00          | 01       | 11       | 10 | 00 | 01 | 11 | 10  |

| <b>①</b> | 000                           | <b>①</b>    | 3        |          | 0  | 0  | -  | 0  | 0   |

| 3        | 001                           | 3           | 3        | γ        | 1  | 1  | 1  | 1  | ~   |

| 4        | 011                           | α           | <b>4</b> | <b>4</b> | ■  | 1  | 1  | 0  | 1   |

| α        | 010                           | 1           | -        | 4        | 4  | -  | -  | 0  | -   |

| β        | 100                           | -           | -        | -        | -  | -  | -  | -  | - 1 |

| γ        | 101                           | -           | -        | 2        | -  | -  | -  | 1  | -   |

| 20       | 111                           | 5           | 4        | 2        | 2  | 0  | 1  | 1  | 0   |

| 3        | 110                           | 3           | (3)      | (3)      | α  | 0  | 1  | 1  | - ] |

Las transiciones  $\mathbf{2} \to \mathbf{4}$  y  $\mathbf{2} \to \mathbf{5}$  son directas. La transición  $\mathbf{3} \to \mathbf{1}$ , es directa, pero  $\mathbf{3} \to \mathbf{\gamma} \to \mathbf{2} \to \mathbf{2}$  sigue un ciclo a través de  $\mathbf{\gamma}$ , Las otras anotaciones se llenan de un modo similar. Es poco usual que se necesiten todas las entradas de renglón de reserva, dando como resultado muchos opcionales (redundancias).

Hasta ahora, se ha dicho poco con respecto a las asignaciones de salidas correspondientes a estados inestables. Hay algunas reglas que se deben seguir, y se presentan a continuación. Las anotaciones de salida para los estados de transición se deben escoger de manera que se eliminen pulsaciones accidentales. Si se desea que la salida sea igual antes y después de la transición, esta debe mantenerse constante a lo largo del ciclo. Si la salida debe cambiar, debe hacerlo solo una vez durante un ciclo, de donde, puede ser opcional para un solo estado de transición durante un ciclo. En la figura anterior considere la transición de 4 de la segunda columna a 1 de la primera columna, transición que sigue un ciclo a través de x. Si se hace que las dos salidas de transición sean opcionales, como se indica a continuación, el resultado puede ser un impulso momentáneo de 1.

States:

$$\textcircled{4} \rightarrow \alpha \rightarrow 1 \rightarrow \textcircled{1}$$

Output:  $1 - 0$

Este 1 momentáneo, dependiendo del agrupamiento de las redundancias puede quedar de la siguiente forma:

$$\underbrace{4}_{1} \rightarrow \alpha \rightarrow 1 \rightarrow \underbrace{1}_{0}$$

Para evitar esto, el primer estado de transición debe especificarse como 1, o bien, el segundo debe ser 0. Estas dos alternativas de muestran en las siguientes figuras:

States:

$$\textcircled{4} \rightarrow \alpha \rightarrow 1 \rightarrow \textcircled{1}$$

$\textcircled{4} \rightarrow \alpha \rightarrow 1 \rightarrow \textcircled{1}$  Output:  $1 \quad 1 \quad - \quad 0 \quad 1 \quad - \quad 0 \quad 0$

Se elige entre estas dos alternativas, tomando la que produzca ecuaciones de salida más simples.

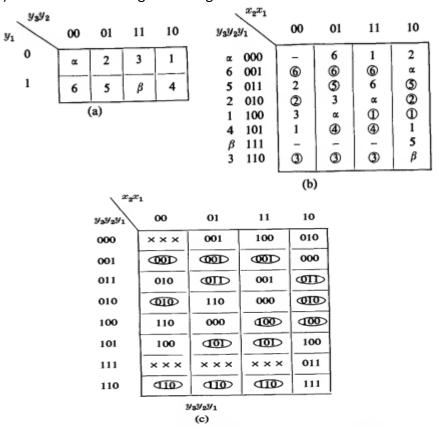

La tabla de transición se sigue directamente a partir de la tabla de estado aumentada, substituyendo cada estado con la combinación de variables de estado correspondiente, como se señala en la siguiente figura:

| $\sqrt{x_2x}$            | 1                          |                            |                          |                   |  |  |

|--------------------------|----------------------------|----------------------------|--------------------------|-------------------|--|--|

| $y_3y_2y_1$              | 00                         | 01                         | 11                       | 10                |  |  |

| 000<br>001<br>011<br>010 | 000<br>001<br>010<br>000   | 001<br>(GE)<br>(X × ×      | 010<br>101<br>011<br>011 | 000<br>000<br>011 |  |  |

| 100<br>101<br>111<br>110 | ×××<br>×××<br>110<br>(110) | ×××<br>×××<br>011<br>(110) | ×××<br>111<br>(B)        | ×××<br>×××<br>010 |  |  |

| $Y_3Y_2Y_1$              |                            |                            |                          |                   |  |  |

# **Ejemplo:**

Obtener una asignación de estado, libre de carrera crítica, para la tabla de la siguiente figura:

| $x_1x_2$ |    |             |             |        |

|----------|----|-------------|-------------|--------|

|          | 00 | 01          | 11          | 10     |

|          | 3  | 6           | 0           | 0      |

|          | 2  | 3           | 1           | ②<br>5 |

|          | 3  | (3)         | 3           | 5      |

|          | 3  | 3<br>4<br>5 | ③<br>④<br>6 | 1      |

|          | 2  | (3)         | 6           | 5      |

|          | 6  | 6           | 6           | 2      |

#### Solución:

Los conjuntos de destino son (1, 3, 4) (2, 5) (6), (1, 6) (2, 3) (4) (5), (1, 2) (3) (4) (5, 6) y (1, 4) (2, 6) (3, 5). Primero se observa un conjunto de destino con más de dos miembros (1, 3, 4) en el primer renglón. En tales casos, a menudo se puede establecer un ciclo dentro del conjunto de destino, por ejemplo  $\mathbf{1} \to \mathbf{4} \to \mathbf{3}$  ó  $\mathbf{4} \to \mathbf{1} \to \mathbf{3}$ . Tomando en cuenta la flexibilidad que ofrecen estos ciclos, generalmente se considera más apropiado tomar en cuenta primero los conjuntos de destino de dos miembros. En este caso, se observa que el estado  $\mathbf{2}$  es un miembro de cuatro conjuntos de esta índole (2, 5) (2, 3) (1, 2) (2, 6). En una asignación de tres estados, un solo estado puede ser adyacente a solo tres estados, de manera que estos cuatro estados de destino requieren que  $\mathbf{2}$  sea adyacente a uno de los estados, de reserva, que se designara como  $\alpha$ . De los cuatro estados que forman pares con  $\mathbf{2}$  en los conjuntos de destino,  $\mathbf{5}$  y  $\mathbf{6}$  no forman parte del conjunto (1, 3, 4) de manera que se les coloca en un lugar adyacente al par  $(2, \alpha)$ , dando la asignación inicial que se muestra en la siguiente figura:

| $y_{1}^{y_{3}y_{2}}$ | 00 | 01 | 11 | 10 |

|----------------------|----|----|----|----|

| 0                    | α  | 2  | T  |    |

| 1                    | 6  | 5  |    |    |

El estado restante que forma para con **2**, **1** y **3** debe ser adyacente a **2** o a  $\alpha$ , de manera que se ubican como indica el siguiente gráfico:

| α | 2 | 3 | 1 |

|---|---|---|---|

| 6 | 5 |   |   |

Por último, observando que el estado **4** puede seguir un ciclo a **3**, pasando por el estado **1**, se coloca un 1 y el estado de reserva restante,  $\beta$ , como se ve a continuación:

| α | 2 | 3 | 1 |

|---|---|---|---|

| 6 | 5 | β | 4 |

A continuación, se verifican los conjuntos de destino para todas las columnas para cuidar que todas las transiciones se puedan efectuar sin carreras críticas con las asignaciones mostradas en los tres últimos diagramas.

El desarrollo de la asignación (a), la tabla de estado aumentada (b) y la tabla de transición (c) se muestra en las siguientes figuras:

Riesgos en circuitos secuenciales.

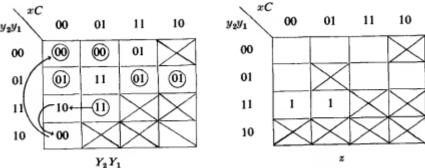

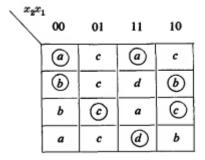

En la siguiente figura se muestra una tabla de flujo y una tabla de transición de un circuito secuencial. El mismo está libre de carreras críticas, de manera que se puede suponer que funcionará adecuadamente.

| $x_2x_1$                                    |            |            |    |          |  |  |  |

|---------------------------------------------|------------|------------|----|----------|--|--|--|

| <i>y</i> <sub>2</sub> <i>y</i> <sub>1</sub> | 00         | 01         | 11 | 10       |  |  |  |

| 00                                          | @          | @          | @  | đ        |  |  |  |

| 01                                          | <b>(b)</b> | <b>(b)</b> | а  | <b>6</b> |  |  |  |

| 11                                          | d          | ь          | 0  | 0        |  |  |  |

| 10                                          | а          | @          | с  | @        |  |  |  |

| \ x₂x                         |                |                |     |            |

|-------------------------------|----------------|----------------|-----|------------|

| y <sub>2</sub> y <sub>1</sub> | 00             | 01             | 11  | 10         |

| 00                            | @              | <b>®</b>       | 00  | 10         |

| 01                            | <u>(1)</u>     | <b>(1)</b>     | 00  | <u>(1)</u> |

| 11                            | 10             | 01             | (1) | (1)        |

| 10                            | 00             | (10)           | 11  | 10         |

|                               | Y <sub>2</sub> | Y <sub>1</sub> |     |            |

Las ecuaciones para las variables de estado son:

$$Y_2 = y_2 x_2 + y_2 \bar{y}_1 x_1 + \bar{y}_1 x_2 \bar{x}_1 + y_2 y_1 \bar{x}_1$$

$$Y_1 = \bar{y}_2 \bar{x}_2 y_1 + y_2 y_1 x_1 + y_2 x_2 x_1 + y_1 x_2 \bar{x}_1$$

El circuito lógico para  $Y_1$  se muestra en el siguiente gráfico.  $Y_2$  se muestra solo en forma simbólica, ya que no es pertinente al estudio actual.

Supongamos que el circuito se encuentra en el estado estable  ${\bf c}$  con  $y_2y_1x_2x_1=1111$ . Bajo esta condición las dos compuertas  $A_2$  y  $A_3$  desarrollarán un 1 en su salida, produciendo  $Y_1=1$  en la salida de la compuerta OR. Ahora se hará que  $x_1$  cambie a 0. En este caso se observa que el circuito debe pasar del estado estable  ${\bf c}$  con  $y_2y_1x_2x_1=110$ , es decir,  $Y_1$  o  $Y_2$  no deben cambiar. Sin embargo, a continuación, se examinará más detalladamente la acción del circuito. Cuando  $x_1$  pasa a 0, las salidas de las compuertas  $A_2$  y  $A_3$  pasan a 0, y la salida de la compuerta  $A_4$  pasa a 1, debido a que  $\overline{x1}$  pasa a 1. No obstante, debido al retardo del inversor,  $\overline{x1}$  no pasará a 1 tan rápidamente como  $x_1$  pasa a 0, de manera que probablemente se tendrá un corto intervalo de tiempo cuando las salidas de todas las compuertas AND sean 0. Puesto que  $y_2$  no cambia, el circuito verá momentáneamente la entrada de la variable de estado  $y_2y_1=10$  y podrá efectuar una transición errónea al estado estable  ${\bf d}$  con  $y_2y_1x_2x_1=1010$ .

A continuación, se supondrá que se tiene el mismo estado inicial  $y_2y_1x_2x_1 = 1111$ , y luego se hará que  $x_2$  pase a 0. Ahora, el circuito debe pasar a través del estado inestable b al estable b cuando  $y_2y_1x_2x_1 = 0101$ . En este caso, vuelve a suceder que  $Y_1$  no debe cambiar. Al igual que antes, las compuertas  $A_2$  y  $A_3$  son 1 inicialmente. Cuando  $x_2$  pasa a 0, la compuerta  $A_3$  pasa a 0, y simultáneamente se inicia una transición en  $Y_2$ . Después del retardo debido a la lógica de  $Y_2$ ,  $Y_2$  pasa a 0 haciendo que  $A_2$  pase a 0 y  $A_1$  llegue a 1 debido a que  $\overline{y2}$  pase a 1. Sin embargo, al igual que antes, el retardo a través del inversor

hará que todas las compuertas sean 0 momentáneamente, haciendo a su vez que  $Y_1$  pase a 0, también momentáneamente. Por lo tanto, el circuito puede efectuar una transición equivocada a **a** estable con  $y_2y_1x_2x_1 = 0001$ .

Los anteriores son ejemplos de funciones equivocadas provocadas por **riesgos estáticos.**

Sea una transición de estado en un circuito en la modalidad fundamental tal, que se requieren una, o más variables secundarias para mantenerlo constante. Si debido a los retardos desiguales del circuito, es posible que una o más variables de estado constantes cambien momentáneamente, entonces se dice que existe un **riesgo estático.**

Los riesgos estáticos son inherentes a la lógica combinacional. En el diseño combinacional normal o en circuitos de reloj o pulso, estos riesgos estáticos no constituyen una preocupación. Sin embargo, si una señal momentáneamente incorrecta se realimenta nuevamente a la entrada, como sucedió en el caso anterior, se puede producir un error permanente.

Un ejemplo de riesgo estático se ve claramente en la siguiente figura:

En el primer caso, el cambio registrado en  $x_1$  hace que el circuito salgo de los cubos  $y_2y_1x_1$  y  $y_2x_2x_1$ , de manera que pasen al cubo  $y_1x_2\overline{x1}$ . En el segundo caso, el cambio registrado en  $x_2$  hace que el circuito salga del cubo  $y_2y_1x_1$  y pase al cubo  $\overline{y2}$   $\overline{x2}$   $y_1$ . Como se observó, el circuito sale de los cubos iniciales con mayor rapidez que con la que entra a los cubos finales. Cada cubo representa una entrada de producto a la compuerta OR de salida. Uno de los términos de producto debe ser 1 para producir una salida en 1. Siempre que el circuito debe pasar de un cubo a otro, existe la posibilidad de un intervalo momentáneo cuando ninguno de los productos correspondientes se encuentra en 1. Tomando esto como base, la solución es bastante evidente. Es necesario que cualquier par de unos entre los que se puede realizar la transición, se encuentren dentro de un solo cubo. Por ende, los dos riesgos de este ejemplo se pueden eliminar, añadiendo dos cubos más, como se ilustra en la siguiente figura:

Se observa que existe otro riesgo estático entre los unos de  $y_2y_1x_2x_1 = 0100$  y  $y_2y_1x_2x_1 = 0110$ , de manera que estos dos unos deben encontrarse también dentro un solo cubo. Por otro lado, los unos de  $y_2y_1x_2x_1 = 0110$  y  $y_2y_1x_2x_1 = 1110$ , no necesariamente deben estar dentro de un solo cubo. De acuerdo con la tabla de flujo, se observa que estos dos unos corresponden a estados estables, y las transiciones verticales entre estados estables son imposibles en los circuitos que operan en modalidad fundamental. Por lo tanto, la realización mínima libre de riesgos estáticos se muestra en la siguiente figura:

El circuito resultante tendrá dos compuertas AND más que el original, pero quedará libre de riesgos.

Hasta ahora vimos que un riesgo estático es una transición no deseada al valor lógico contrario al que tiene que proporcionar el circuito, por ejemplo, cuando la salida debe ser constantemente 0 y tiene una transición no deseada a 1, o viceversa.

También se puede presentar un riesgo cuando la salida cambia. Cuando ocurren ciertos patrones de retardo, es probable que el circuito pase momentáneamente al nuevo valor y luego, retorne al valor inicial antes de efectuar la transición permanente, es decir por ejemplo  $0 \to 1 \to 0 \to 1$  en lugar de  $0 \to 1$ . Esta situación se conoce como **riesgo dinámico**.

Por suerte hay un teorema que dice:

Un circuito de dos niveles escrito como SdP que esté libre de todos los riesgos estáticos en los unos, estará libre también de todos los riesgos estáticos y dinámicos.

Hay otro tipo de riesgo que se presenta solamente en circuitos secuenciales y se llama **riesgo esencial.** Este tipo de riesgo no se puede resolver agregando compuertas como en el caso de los riesgos estáticos. Un riesgo esencial se presenta cuando los retardos producen un cambio de excitación, antes que los circuitos que generan otra excitación detecten incluso el cambio de la entrada.

Este comportamiento se producirá si dos columnas adyacentes cualesquiera de la tabla de estado presentan uno de los patrones que se ilustran en la siguiente figura:

Un **riesgo esencial** se puede detectar en una tabla de estado, cuando se tiene un estado estable del cual, tres cambios consecutivos en una sola variable de entrada llevan el circuito a un estado diferente al del primer cambio solo.

Mirando la figura (b) anterior se ve que, si partimos del estado estable **1**, un solo cambio de variable lo llevará a **2**, y dos cambios más lo llevarán a **4**.

Dado que este tipo de riesgos esenciales **no se pueden eliminar modificando la lógica,** la única forma de controlarlos es manejando el número de compuertas de cada aro de realimentación. Esto excede nuestro apunte, pero comentaremos que cuando más compuertas pertenezcan a un mismo chip tendrán menos probabilidad de presentar estos problemas, ya que sus retardos y su temperatura de trabajo serán semejantes.

## **Ejemplo:**

Diseñar un circuito secuencial asincrónico con dos entradas, **A** y **B**. Y que, además, contenga una salida **Z**, que normalmente tenga el valor **0**. La salida deberá establecerse en **1** cuando se presente una transición de **0** a **1** en **A**, y deberá reestablecerse a **0** siempre que **B** sea **1**.

### Solución:

C.

En la siguiente figura se ilustra una tabla de estado primitiva que satisface las especificaciones del problema:

| AB |     |    |    |    | AB |    |    |    |    |

|----|-----|----|----|----|----|----|----|----|----|

|    | 00  | 01 | 11 | 10 |    | 00 | 01 | 11 | 10 |

| 1  | 1   | 2  | X  | 3  | 1  | 0  |    |    |    |

| 2  | 1   | 2  | 4  | Х  | 2  |    | 0  |    |    |

| 3  | 5   | X  | 4  | 3  | 3  |    |    |    | 1  |

| 4  | X   | 2  | 4  | 6  | 4  |    |    | 0  |    |

| 5  | (5) | 2  | X  | 3  | 5  | 1  |    |    |    |

| 6  | 1   | X  | 4  | 6  | 6  |    |    |    | 0  |

|    |     |    |    |    |    |    |    |    |    |

Simplificando esta tabla de estados llegamos a las siguientes clases de compatibilidad:

La colección cerrada más pequeña es:

A la primera la llamamos  ${\bf a}$ , a la segunda le damos el nombre de  ${\bf b}$  y a la tercera

De esta forma me queda la tabla primitiva mínima de la siguiente forma:

| AB |    |    |     |     | AB |    |    |    |    |

|----|----|----|-----|-----|----|----|----|----|----|

|    | 00 | 01 | 11  | 10  |    | 00 | 01 | 11 | 10 |

| а  | a  | a  | С   | b   | a  | 0  | 0  |    |    |

| b  | Ь  | а  | C   | (ڪ) | b  | 1  |    |    | 1  |

| C  | а  | а  | (6) | (6) | c  |    |    | 0  | 0  |

|    |    |    |     |     |    |    |    |    |    |

Una asignación de estados podría ser la siguiente:

Vemos que no podemos mapear un cubo de orden dos con tres estados, por lo tanto incorporamos un nuevo estado haciendo un ciclo entre los estados  $\bf b$  y  $\bf c$ . Para ello agregamos un estado intermedio  $\bf X$ . Entonces la asignación de estados libre de carreras queda de la siguiente manera:

La tabla de estados ya asignados y su salida se ve en la siguiente figura:

|    |    |    |    |    |    |    |    | U  | U          |

|----|----|----|----|----|----|----|----|----|------------|

| AB |    |    |    |    | AB |    |    |    |            |

|    | 00 | 01 | 11 | 10 |    | 00 | 01 | 11 | 10         |

| 00 | 6  | 00 | 10 | 01 | 00 | 0  | 0  | 0  | 0          |

| 01 | 01 | 00 | 11 | 01 | 01 | 1  | X  | X  | 1          |

| 11 | X  | Х  | 10 | X  | 11 | X  | X  | X  | X          |

| 10 | 00 | 00 | 10 | 10 | 10 | X  | 0  | 0  | <b>(0)</b> |

|    |    |    |    |    |    |    |    |    |            |

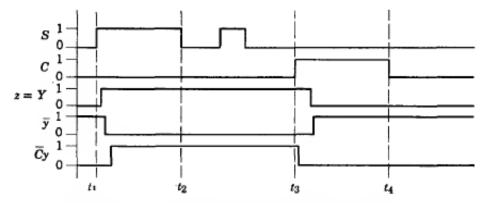

Los mapas de las variables de excitación  $Y_1$  e  $Y_0$  quedan, recordando que arriba ya tenemos el mapa de la salida Z:

|      | AB |    |     |           |    |      | AB |    |    |             |    |  |

|------|----|----|-----|-----------|----|------|----|----|----|-------------|----|--|

| y1y0 |    | 00 | 01  | 11        | 10 | y1y0 |    | 00 | 01 | 11          | 10 |  |

|      | 00 | 0  | 0   | 0         | 1  |      | 00 | 0  | 0  | <b>/1</b> \ | 0  |  |

|      | 01 | 1  | 0   | $\forall$ | 1  |      | 01 | 0  | 0  | 1           | 0  |  |

|      | 11 | X  | ) X | 0         | χ  |      | 11 | Χ  | Х  | 1           | X  |  |

|      | 10 | 0  | 0   | 0         | 0  |      | 10 | 0  | 0  | U           | IJ |  |

|      |    |    |     |           |    |      |    |    |    |             |    |  |

Las ecuaciones finales son:

$$Y_0 = \overline{B}.y_0 + A.\overline{B}.\overline{y1} + A.\overline{y1}.y_0$$

$Y_1 = A.B + A.y_1$

$Z = y_0$

El circuito final lo vemos en el siguiente gráfico: